Fisika

Diunggah oleh

Hafifah Fifa0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

5 tayangan1 halamanHak Cipta

© © All Rights Reserved

Format Tersedia

DOCX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

5 tayangan1 halamanFisika

Diunggah oleh

Hafifah FifaHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 1

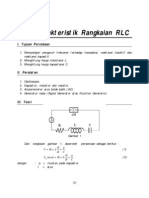

TUJUAN

1. Menentukan beda fase antara arus dengan tegangan yang melintas pada masing-masing

komponen.

2. Melukiskan diagram fasor pada rangkaian RLC seri

TEORI

Rangkalan seri terdiri atas resistor (R), kapasitor (C) dan Induktor (L), dihubungkan dengan sumber

tegangan bolak-balik.

Tegangan sumber: Vs = Vm sin wt dan arus yang sama i = i (t) melalui R, L dan C.

Andaikan persamaan arus yang melalui rangkaian: i = i(t) = im sin (wt - tho) dengan im : arus maksimum.

Tho : beda fase antara arus dan sumber tegangan.

Gambar 1

Dengan memperhatikan beda fase antara arus dan tegangan yang melintas pada masing-masing

komponen dapat dilukis diagram fasor rangkalan RLC seri tersebut.

VR sefase dengan i, dengan harga maksimum VmR = im.R

Vc tertinggal phi/2 terhadap i, dengan harga maksimum VmC = im.Xc

VL mendahului phi/2 terhadap i, dengan harga VmL = im.XL

gambar 2

Vs = VR + VC + VL

Harga maksimum dari Vs adalah:

Vm = VR+ (VML-VMC) = √2+(XL-XC =IR²+(XL-X (1)

Anda mungkin juga menyukai

- Gelombang AcDokumen39 halamanGelombang AcDana GayBelum ada peringkat

- ABB RLC SeriDokumen1 halamanABB RLC Serisubarjoachmad2Belum ada peringkat

- Arus BolakDokumen10 halamanArus BolakaryainteristiBelum ada peringkat

- Arus & Tegangan ACDokumen34 halamanArus & Tegangan ACRatna Tri MharaniBelum ada peringkat

- MODUL 02 Menganalisis Rangkaian ListrikDokumen26 halamanMODUL 02 Menganalisis Rangkaian ListrikabukayyisBelum ada peringkat

- Alternating CurrentDokumen13 halamanAlternating CurrentWah YunaBelum ada peringkat

- Arus Bolak BalikDokumen14 halamanArus Bolak BalikFerryBelum ada peringkat

- Arus Bola BalikDokumen5 halamanArus Bola BalikSurya Pro MildBelum ada peringkat

- RLC SeriDokumen13 halamanRLC SeriАлпианорBelum ada peringkat

- Arus Listrik Bolak BalikDokumen10 halamanArus Listrik Bolak BalikAriepamungkazBelum ada peringkat

- Analisis SinusoidaDokumen9 halamanAnalisis SinusoidaIkhsan WijayantoBelum ada peringkat

- Resonansi RangkaianDokumen26 halamanResonansi RangkaianLailatul KhairiahBelum ada peringkat

- Ac DCDokumen12 halamanAc DCNjsgBelum ada peringkat

- Bab Vi Rangkaian Listrik Bolak-BalikDokumen36 halamanBab Vi Rangkaian Listrik Bolak-BalikSmalgebraBelum ada peringkat

- Arus Bolak BalikDokumen12 halamanArus Bolak BalikLaila Simpson BlueBelum ada peringkat

- RLCDokumen9 halamanRLCChomsatin Amalia100% (1)

- 9 - Arus ACDokumen24 halaman9 - Arus ACJihandini Rhodiya Ahyary100% (1)

- Modul Revisi Bab I, IIDokumen30 halamanModul Revisi Bab I, IIM RaynaldiBelum ada peringkat

- Arus Bolak-BalikDokumen12 halamanArus Bolak-BalikNI MADE AYU WULANDARIBelum ada peringkat

- Rangkaian Arus Bolak-Balik (Fisika)Dokumen24 halamanRangkaian Arus Bolak-Balik (Fisika)AraraBelum ada peringkat

- Review Buku 1Dokumen6 halamanReview Buku 1Esteria ChristinaBelum ada peringkat

- Ph203 CH23 WorksheetDokumen10 halamanPh203 CH23 WorksheetEko Bambang SaputroBelum ada peringkat

- L3Dokumen4 halamanL3Puji Selamet IswantoBelum ada peringkat

- Arus Bolak BalikDokumen20 halamanArus Bolak Balik21etkishaBelum ada peringkat

- Topik 3RL221Dokumen7 halamanTopik 3RL221Farida Ayu lestariBelum ada peringkat

- Listrik ACDokumen9 halamanListrik ACBrillianty FanggidaeBelum ada peringkat

- Handout RLDokumen98 halamanHandout RLTaufiq TaqimBelum ada peringkat

- Arus Bolak-Balik FixDokumen22 halamanArus Bolak-Balik FixAlia RizkiBelum ada peringkat

- Modul IV (Resonansi Listrik)Dokumen8 halamanModul IV (Resonansi Listrik)Den L IdentBelum ada peringkat

- Buku Rangkaian Elektrik II - Hery PDokumen145 halamanBuku Rangkaian Elektrik II - Hery PFirly Azka N100% (1)

- Soal Modul Tutorial 6 FIDAS IIA 2020-2021Dokumen2 halamanSoal Modul Tutorial 6 FIDAS IIA 2020-2021Salma AzzahraBelum ada peringkat

- Listrik ACDokumen13 halamanListrik ACBerty SultanBelum ada peringkat

- Menerapkan Dasar-Dasar KelistrikanDokumen11 halamanMenerapkan Dasar-Dasar KelistrikanDhike Marshylia100% (1)

- Rangkaian Listrik Arus Bolak Balik LanjutanDokumen33 halamanRangkaian Listrik Arus Bolak Balik LanjutanRinaldi PraharsamahasiswaBelum ada peringkat

- Persamaan KontinuitasDokumen3 halamanPersamaan Kontinuitassman 4 pekalonganBelum ada peringkat

- MOD 1 (Arus Dan Tegangan Bolak-Balik)Dokumen11 halamanMOD 1 (Arus Dan Tegangan Bolak-Balik)Toyama YuukiBelum ada peringkat

- Rangkaian Arus Dan Tegangan AcDokumen15 halamanRangkaian Arus Dan Tegangan AcSiti Fahriyah HidayatiBelum ada peringkat

- MATERI Rangkaian Arus Bolak BalikDokumen7 halamanMATERI Rangkaian Arus Bolak BalikB. Tiara Shafa ZahirahBelum ada peringkat

- Listrik Arus Bolak BalikDokumen6 halamanListrik Arus Bolak BalikSury GitaBelum ada peringkat

- Sodapdf Converted Bab. 5 Arus Bolak BalikDokumen19 halamanSodapdf Converted Bab. 5 Arus Bolak BalikJokiuy TyruwBelum ada peringkat

- Jbptunikompp GDL Taufiknuzw 19441 6 HukumkiDokumen9 halamanJbptunikompp GDL Taufiknuzw 19441 6 HukumkiM Emmulsen SujamukhBelum ada peringkat

- TUGAS RANGKAIAN RLC Seri OkDokumen3 halamanTUGAS RANGKAIAN RLC Seri OkI Gusti Nyoman Anton Surya DiputraBelum ada peringkat

- Rangkaian Arus Bolak BalikDokumen21 halamanRangkaian Arus Bolak BalikSyah RoniBelum ada peringkat

- Rangkaian Gabungan RLCDokumen17 halamanRangkaian Gabungan RLCmeliana314Belum ada peringkat

- Percobaan RLC SeriDokumen4 halamanPercobaan RLC SeriAbdulloh KhoironyBelum ada peringkat

- MATERI Arus Bolak BalikDokumen4 halamanMATERI Arus Bolak BalikB. Tiara Shafa ZahirahBelum ada peringkat

- Rangkaian Arus Dan Tegangan AcDokumen15 halamanRangkaian Arus Dan Tegangan Aczulham tanjungBelum ada peringkat

- Rangkaian Transien Kondisi AwalDokumen10 halamanRangkaian Transien Kondisi AwalFitri handayaniBelum ada peringkat

- Rangkaian Listrik IIDokumen9 halamanRangkaian Listrik IIIlham JuniusBelum ada peringkat

- Diktat TTL - 4Dokumen17 halamanDiktat TTL - 4Fadhil AlfathBelum ada peringkat

- Arus Bolak BalikDokumen14 halamanArus Bolak Balikbun bunBelum ada peringkat

- M1 - P2 - Kuliah 2021Dokumen10 halamanM1 - P2 - Kuliah 2021Alfridus NahakBelum ada peringkat

- Fisika SINDY AMALIAHDokumen8 halamanFisika SINDY AMALIAHSindy AmaliahBelum ada peringkat

- RPP Arus Bolak-BalikDokumen24 halamanRPP Arus Bolak-BalikIntan Mustika NspBelum ada peringkat

- Ardya Ajeng Pramesti E.W - Laporan Akhir Percobaan 6Dokumen37 halamanArdya Ajeng Pramesti E.W - Laporan Akhir Percobaan 6Komang Aldi Rae GunawanBelum ada peringkat

- 9rangkaianarusbolakbalik-161130235942 PDFDokumen70 halaman9rangkaianarusbolakbalik-161130235942 PDFLuthfi Arifandi Yk100% (1)

- Arus Bolak Balik 2Dokumen22 halamanArus Bolak Balik 2Nuraeni EnayBelum ada peringkat

- ABB Metode PhasorDokumen27 halamanABB Metode PhasorRayven HanjayaBelum ada peringkat

- Panduan PSAJ XII 2024Dokumen1 halamanPanduan PSAJ XII 2024Hafifah FifaBelum ada peringkat

- Latihan Soal-Soal 12Dokumen8 halamanLatihan Soal-Soal 12Hafifah FifaBelum ada peringkat

- Pai Bab 4Dokumen7 halamanPai Bab 4Hafifah FifaBelum ada peringkat

- Jadwal Pas & Sas Ganjil 2023Dokumen1 halamanJadwal Pas & Sas Ganjil 2023Hafifah FifaBelum ada peringkat

- Latihan 1 Pai Kelas Xii 23-24Dokumen24 halamanLatihan 1 Pai Kelas Xii 23-24Hafifah FifaBelum ada peringkat

- Metode Ilmiah Fiks 1Dokumen7 halamanMetode Ilmiah Fiks 1Hafifah FifaBelum ada peringkat