Register Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh Beberapa

Diunggah oleh

Yusup Nugraha0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

177 tayangan4 halamanJudul Asli

Register adalah suatu rangkaian logika yang dibentuk oleh beberapa.docx

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOCX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

177 tayangan4 halamanRegister Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh Beberapa

Diunggah oleh

Yusup NugrahaHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 4

Register adalah suatu rangkaian logika yang

dibentuk oleh beberapa flip-flop atau bistabil

multivibrator (JK flip atau D flip-flop) yang disusun

sedemikian rupa sehingga mampu menyimpan

dan memproses informasi dalam bentuk biner.

Jumlah flip-flop yang digunakan bergantung pada

banyaknya bit dari informasi yang akan disimpan

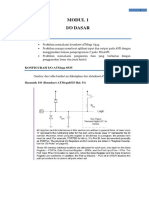

atau diproses. Sebagai contoh register yang Pada gambar di atas nilai dari input J dan K

terdapat pada komputer digital (mini computer) tergantung pada output Q dan not Q pada

biasanya terdiri dari 16 bit. rangkaian counter. Jika input C (clock) = 1, maka

informasi yang berada pada output counter (yang

Menurut fungsinya register dapat dibedakan masuk ke input register J dan K) akan berpindah

menjadi dua macam: ke output storage register (Q0, Q1, Q2, Q3).

1. Storage register Selanjutnya jika input C (clock) berubah menjadi

2. Shift register 0, maka informasi tadi akan tetap tersimpan

Storage Register walaupun output counter (yang masuk ke input

register J dan K) berubah nilainya.

Untuk membuat storage register kita dapat

memanfaatkan flip flop jenis D Flip flop dan JK Shift Register

flip-flop. Karena D flip flop dan JK flip flop

Seperti yang sudah dijelaskan di atas bahwa

kerjanya dapat menyimpan 1 bit bilangan biner,

register dibentuk dari beberapa buah flip-flop

maka kedua jenis flip flop ini dapat kita gunakan

yang mampu menyimpan informasi dalam

untuk storage register. Untuk membentuk

bilangan biner (0 atau 1). Setiap bit informasi

rangkaian register yang mampu menyimpan 4 bit

akan diwakili oleh satu buah flip flop atau bistabil

diperlukan empat buah flip flip dalam jenis yang

multivibrator ( D flip-flop atau JK flip-flop).

sama. Berikut ini adalah contoh pengunaan D

Dengan menghubungkan flip-flop sedemikian

Flip - flop untuk membuat rangkaian storage

rupa kita dapat membuat informasi bisa

register.

dimasukkan untuk disimpan sementara dan bisa

dikeluarkan juga bilamana diperlukan. Register

yang bisa melakukan fungsi seperti di atas

deisebut dengan shift register.

1. SISO (Serial Input Serial Output

Gambar Register SISO yang menggunakan

JK FF

Pada rangkaian di atas, informasi atau data yang

masuk pada input D0, D1, D2, dan D3 biasanya

datang dari rangkaian counter atau pencacah.

Jika input clock diberika harga 0, maka informasi

apapun yang berada pada input D tidak akan

mempengaruhi nilai pada output Q. Akan tetapi, Prinsip kerja:

jika input clock (CLK) diberi nilai 1 maka output Q Informasi/data dimasukan melalui word in dan

akan sama nilainya dengan input D dan

seterusnya. Jika input clock (CLK) kembali akan dikeluarkan jika ada denyut lonceng berlalu

menjadi 0, maka informasi terakhir akan tetap

dari 1 ke 0. Karena jalan keluarnya flip-flop satu

tersimpan pada output Q walaupun input D

nilainya berubah-ubah. Untuk membersihkan dihubungkan kepada jalan masuk flip-flop

(refresh) isi memory dapat digunakan input clear.

Sedangkan untuk membentuk storage register berikutnya, maka informasi didalam register akan

dari JK flip flop, maka kita dapat menyusun digrser ke kanan selama tebing dari denyut

rangkaian JK flip-flip seperti terlihat pada gambar

berikut ini. lonceng (Clock).

Tabel Kebenaran (Misal masuknya 1101) berikutnya sehingga dengan proses ini terjadi

Clock ke Word in Q1 Q2 Q3 Q4

pergeseran ke kanan.

0 0 0 0 0 0 TABEL KEBENARAN (jika input 1101)

1 1 1 0 0 0 Clock ke Input Q1 Q2 Q3 Q4

2 0 0 1 0 0 0 0 0 0 0 0

3 1 1 0 1 0 1 1 1 0 0 0

4 1 1 1 0 1 2 1 1 1 0 0

Register geser SISO ada dua macam yaitu: 3 0 0 1 1 0

4 1 1 0 1 1

a) Shift Right Register (SRR)/Register geser kanan

Informasi digit digeser kekanan setiap ada

b) Shift Left Register (SLR)/Register geser kiri

perubahan pulsa clock tebing atas. Geser kanan

c) Shift Control Register dapat berfungsi sebagai SSR

berfungsi sebagai operasi aritmatika yaitu pembagi

maupun SLR

dua untuk tiap-tiap flip-flop.

Rangkaian Shift control adalah sebagi berikut:

Jika SC = 1 , maka akan mengaktifkan input geser

kiri. Output NAND masuk ke input D-FF4 dan

setelah diberi pulsa clock informasi dikeluarkan

melalui Q4 dan keluaran Q4 dihubungkan ke input

D-FF3, keluaran D-FF3 dimasukan ke D-FF

berikutnya, sehingga dengan demikian terjadi

Rangkaian ini untuk mengaktifkan geser kanan/kiri pergeseran informasi bit ke arah kiri.

yang ditentukan oleh SC. Jika SC=1, maka akan TABEL KEBENARAN (jika input 1101)

Clock

mengaktifkan SLR. Jika SC=0, maka akan Input Q1 Q2 Q3 Q4

ke

mengaktifkan SRR. Gambar rangkaian 0 0 0 0 0 0

1 1 0 0 0 1

selengkapnya adalah sebagai berikut:

2 1 0 0 1 1

3 0 0 1 1 0

4 1 1 1 0 1

Register geser kiri berfungsi sebagai operasi

aritmatika yaitu sebagai pengali dua untuk tiap-tiap

flip-flop.

2. Register Geser SIPO Serial Input Pararel

Output

Keterangan: Adalah register geser dengan masukan data

Jika SC=0,maka input geser kanan akan aktif. secara serial dan keluaran data secara parelel.

Keluaran NAND diumpamakan ke input DFF1 dan Gambar rangkaiannya adalah sebagai berikut:

setelah denyut lonceng berlaku (saat tebing (SIPO menggunakan D-FF)

depan), maka informasi diteruskan ke output Q1.

Dan output Q1 terhubung langsung keoutput DFF2

Sebelum dimasuki data rangkaian direset dulu agar

keluaran Q semuanya 0. Setelah itu data dimasukkan

secara paralel pada input D-FF dan data akan

diloloskan keluar secara paralel setelah flip-flop

mendapat pulsa clock dari 0 ke 1.

Cara kerja: Contoh:

Masukan-masukan data secara deret akan TABEL KEBENARAN:

Cloc D1 D2 D3 QD QC QB

dikeluarkan oleh D-FF setelah masukan denyut

k D4 QA

lonceng dari 0 ke 1. Keluaran data/informasi 0 1101 0000

1 1101 1101

serial akan dapat dibaca secara paralel setelah

2 1001 1001

diberikan satu komando (Read Out). Bila dijalan 3 0001 0001

masuk Read Out diberi logik 0, maka semua 4. Register geser PISO Paralel Input Serial

keluaran AND adalah 0 dan bila Read Out diberi Output

logik 1, maka pintu-pintu AND menghubung Adalah register geser dengan masukan data

langsungkan sinyal-sinyal yang ada di Q masing- secara paralel dan dikeluarkan secara

masing flip-flop. deret/serial.

Contoh: Bila masukan data 1101 Gambar rangkaian register PISO menggunakan

TABEL KEBENARANNYA: D-FF adalah sebagai berikut:

Read Q1 Q2Q3 Q4 A B CD

Clock Input

Out

0 0 0 0000 0000

0 1 1 1000 0000

0 2 1 1100 0000

0 3 0 0110 0000

0 4 1 1011 0000

1 1011 1011

3. Register Geser PIPO Paralel Input Paralel

Outpu

Adalah register geser dengan masukan data secara

Rangkaian diatas merupakan register geser

jajar/paralel dan keluaran jajar/paralel.

dengan panjang kata 4 bit. Semua jalan masuk

Gambara rangkaiannya adalah sebagai berikut:

clock dihubungkan jajar. Data-data yang ada di

(PIPO menggunakan D-FF)

A, B, C, D dimasukkan ke flip-flop secara

serempak, apabila dijalan masuk Data Load

diberi logik 1.

Cara Kerja:

§ Mula-mula jalan masuk Data Load = 0, maka

semua pintu NAND mengeluarkan 1, sehingga

Cara kerja:

jalan masuk set dan rerset semuanya 1 berarti

bahwa jalan masuk set dan reset tidak

berpengaruh.

§ Jika Data Load = 1, maka semua input paralel akan

dilewatkan oleh NAND. Misal jalan masuk A=1,

maka pintu NAND 1 mengeluarkan 0 adapun

pintu NAND 2 mengeluarkan 1. Dengan demikian Rangkaian selengkapnya adalah sbb:

flip-flop diset sehingga menjadi Q=1. Karena flip-

flop yang lainpun dihubungkan dengan cara yang

sama, maka mereka juga mengoper informasi

pada saat Data Load diberi logik 1. Setelah

informasi berada didalam register, Data Load

diberi logik 0. Informasi akan dapat dikeluarkan

dari register dengan cara memasukkan denyut

lonceng, denyut-demi denyut keluar deret/seri. Catatan:

Untuk keperluan ini jalan masuk D dihubungkan

Jika IC=0, maka input yang dimasukan ke D0, D1, D2, D3 tidak

kepada keluaran Q. mempengaruhi keadaan output QA, QB, QC, QD

Ada juga register yang dapat digunakan sebagai tetapi yang mempengaruhinya adalah data yang

Shift register SISO maupun PIPO dengan dimasukkan ke input D-FF secara serial, maka

bantuan suatu control sbb: pada kondisi ini rangkaian akan bekerja senagai

register geser SISO.

Jika IC=1, maka input yang dimasukkan ke gate D seri tidak

akan mempengaruhi output, tetapi output

Input Control = 0, berfungsi sebagai register dipengaruhi oleh data paralel (D0, D1, D2, D3).

geser SISO Input dimasukkan secara serempak dan keluaran

Input Control = 1, berfungsi sebagai register ditunjukkan secara serempak begitu pulsa clock

geser PIPO berguling dari 1 ke 0, maka pada kondisi ini

Data IC Preset Reset

0 1 1 0 rangkaian akan bekerja sebagai registeer geser

1 1 0 1 PIPO.

0 0 1 1

1 0 1 1

Rangkaian kontrol diatas dapat disimbolkan sbb:

Anda mungkin juga menyukai

- Shift RegisterDokumen9 halamanShift RegisterIkhsanul ArifBelum ada peringkat

- Shift RegisterDokumen9 halamanShift RegisterAgus Nugraha Gee'narsaBelum ada peringkat

- Digital CounterDokumen14 halamanDigital CounterAdi YuniarBelum ada peringkat

- Jurnal p1Dokumen7 halamanJurnal p1Lalu Wir Hanan HadiBelum ada peringkat

- Laporan AdderSubtractorFIKSDokumen21 halamanLaporan AdderSubtractorFIKSAyu NingrumBelum ada peringkat

- ENCODER FUNGSI DAN JENISDokumen17 halamanENCODER FUNGSI DAN JENISFieve KmanBelum ada peringkat

- Rangkaian Flip Flop SRDokumen10 halamanRangkaian Flip Flop SRIrvan NdooBelum ada peringkat

- Laporan Praktikum Modul 5Dokumen19 halamanLaporan Praktikum Modul 5Reyan Qowi DzakyprasetyoBelum ada peringkat

- Rangkaian RC SeriDokumen12 halamanRangkaian RC SeriRio kurniawanBelum ada peringkat

- Kutub Empat Dan Kopling Magnetic (DRE)Dokumen29 halamanKutub Empat Dan Kopling Magnetic (DRE)Sam Rizky Pratama100% (1)

- Hukum de MorganDokumen4 halamanHukum de MorganPuja Setiawan20Belum ada peringkat

- RANGKAIAN LOGIKA SEKUENSIAL DAN KOMBINASIONALDokumen9 halamanRANGKAIAN LOGIKA SEKUENSIAL DAN KOMBINASIONALGedmi Sari MelatiBelum ada peringkat

- KARAKTERISTIK BJTDokumen12 halamanKARAKTERISTIK BJTMuhamad AzisBelum ada peringkat

- P2 Flip Flop - Arif Hakam Hidayat (F1B019026) - AccDokumen52 halamanP2 Flip Flop - Arif Hakam Hidayat (F1B019026) - AccArif Hakam HidayatBelum ada peringkat

- DEKODER DAN ENKODERDokumen10 halamanDEKODER DAN ENKODERWilliam FernandesBelum ada peringkat

- TEORI DE MORGAN DAN EXORDokumen7 halamanTEORI DE MORGAN DAN EXORSiti SuparyutiBelum ada peringkat

- Flip FlopDokumen26 halamanFlip Flopwilliam fernandes100% (1)

- Modul 1Dokumen6 halamanModul 1nonameBelum ada peringkat

- Gerbang Logika Nand, Nor, Dan X-OrDokumen8 halamanGerbang Logika Nand, Nor, Dan X-OrAbdul Rohman SayyidBelum ada peringkat

- Teori RS Flip-FlopDokumen8 halamanTeori RS Flip-FlopDoni SahputraBelum ada peringkat

- Laporan Dasar Teknik DigitalDokumen22 halamanLaporan Dasar Teknik DigitalDimo WibowoBelum ada peringkat

- D3-1B-TGS-6-Ahmad Ainur Rofik (Kalkulator Pengurangan)Dokumen13 halamanD3-1B-TGS-6-Ahmad Ainur Rofik (Kalkulator Pengurangan)Farid Amar FuadiBelum ada peringkat

- SynchronousDokumen10 halamanSynchronousika fitrianiBelum ada peringkat

- Counter AsinkronDokumen13 halamanCounter AsinkronWildan Ahmad Muttaqien BillahBelum ada peringkat

- Galih Muhammad Ghufron - 1306619059 - Laporan Akhir (NAND AND NOR SR LATCH)Dokumen14 halamanGalih Muhammad Ghufron - 1306619059 - Laporan Akhir (NAND AND NOR SR LATCH)ghufron galihBelum ada peringkat

- Rangkaian Flip FlopDokumen16 halamanRangkaian Flip FlopKhalif RifkyBelum ada peringkat

- RANGKAIAN FLIP-FLOPDokumen9 halamanRANGKAIAN FLIP-FLOPMaulana AdiBelum ada peringkat

- Rangkaian SekuensialDokumen14 halamanRangkaian SekuensialwahyuBelum ada peringkat

- Transformasi LaplaceDokumen10 halamanTransformasi Laplaceivana angeliaBelum ada peringkat

- Counter Up Dan Counter DownDokumen21 halamanCounter Up Dan Counter DownShiraBelum ada peringkat

- Rangkaian Listrik II Jobsheet 1 Karakteristik Sinyal AC PDFDokumen5 halamanRangkaian Listrik II Jobsheet 1 Karakteristik Sinyal AC PDFIrvandy Ilza NovendraBelum ada peringkat

- Osilator HartleyDokumen5 halamanOsilator HartleyJihan NovitaBelum ada peringkat

- PENCACAH TAK SINKRON DAN SINKRONDokumen1 halamanPENCACAH TAK SINKRON DAN SINKRONEndah FitrianiBelum ada peringkat

- FLIP-FLOPDokumen18 halamanFLIP-FLOPmanzasta0% (1)

- OSILATORDokumen30 halamanOSILATORvliling0% (2)

- Shift RegisterDokumen7 halamanShift RegisterBhayu HerwahyudiBelum ada peringkat

- Serial AdderDokumen5 halamanSerial AdderBhayu HerwahyudiBelum ada peringkat

- EncoderDokumen19 halamanEncoderNoor Muhammad RizkiBelum ada peringkat

- TIMER FLIP-FOP SHIFTDokumen15 halamanTIMER FLIP-FOP SHIFTriyanBelum ada peringkat

- Sedangkan Decade Counter Merupakan Nilai Maksimal Yang Dapat Dicacah Oleh Suatu CounterDokumen4 halamanSedangkan Decade Counter Merupakan Nilai Maksimal Yang Dapat Dicacah Oleh Suatu CounterDwi Puspita ParawangsaBelum ada peringkat

- Half Adder & Full AdderDokumen6 halamanHalf Adder & Full AdderAnonymous 9birR2tIBelum ada peringkat

- Laporan Praktikum 7 - RegisterDokumen12 halamanLaporan Praktikum 7 - RegisterOkkyAdhityaBelum ada peringkat

- Paper The Piano and LED Chaser With IC555Dokumen3 halamanPaper The Piano and LED Chaser With IC555Xu WeimingBelum ada peringkat

- LAPORAN PRAKTIKUM GERBANGDokumen19 halamanLAPORAN PRAKTIKUM GERBANGRadhiyahtul MiftahBelum ada peringkat

- Laporan Praktikum Sistem DigitalDokumen13 halamanLaporan Praktikum Sistem DigitalResy Dwi LarasBelum ada peringkat

- Flip FlopDokumen16 halamanFlip FlopayuBelum ada peringkat

- Laporan Flip Flop-1Dokumen18 halamanLaporan Flip Flop-1MaheniBelum ada peringkat

- Asinkron & Sinkron CounterDokumen17 halamanAsinkron & Sinkron CounterNurwahidBelum ada peringkat

- Rangkaian KombinasiDokumen29 halamanRangkaian KombinasiBagus FatkhurroziBelum ada peringkat

- Asynchronous CounterDokumen14 halamanAsynchronous CounterwenBelum ada peringkat

- Penguat InstrumentasiDokumen7 halamanPenguat InstrumentasiAs'ad ShidqyBelum ada peringkat

- Rangkaian AritmatikaDokumen15 halamanRangkaian AritmatikaFikris RamadhaniBelum ada peringkat

- Osilator, Jembatan Wien, Penggeser Fasa PDFDokumen23 halamanOsilator, Jembatan Wien, Penggeser Fasa PDFlisdianaBelum ada peringkat

- Teori Tambahan Modul 2.2 MikroDokumen7 halamanTeori Tambahan Modul 2.2 MikroCarly DepsenBelum ada peringkat

- Modul 8 SHIFT REGISTERDokumen9 halamanModul 8 SHIFT REGISTERTaufikhutama PutraBelum ada peringkat

- Shift RegisterDokumen7 halamanShift RegisterPandu HardiBelum ada peringkat

- Shift RegisterDokumen12 halamanShift RegisterNi Kadek Sekar Waras SariBelum ada peringkat

- Laporan Praktikum Teknik Digital A RegisterDokumen9 halamanLaporan Praktikum Teknik Digital A RegisterMuh Agung SantosoBelum ada peringkat

- Register Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaDokumen4 halamanRegister Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaYusup NugrahaBelum ada peringkat

- Register Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaDokumen4 halamanRegister Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaYusup NugrahaBelum ada peringkat

- Register Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaDokumen4 halamanRegister Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaYusup NugrahaBelum ada peringkat

- Register Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaDokumen4 halamanRegister Adalah Suatu Rangkaian Logika Yang Dibentuk Oleh BeberapaYusup NugrahaBelum ada peringkat

- Tugas JarkomDokumen11 halamanTugas JarkomYusup NugrahaBelum ada peringkat

- Diktat Plc1Dokumen31 halamanDiktat Plc1andraa_063084Belum ada peringkat