2539-jos-ee-DSP108-06d Kontroler PID DSP PDF

Diunggah oleh

haris kunkunDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

2539-jos-ee-DSP108-06d Kontroler PID DSP PDF

Diunggah oleh

haris kunkunHak Cipta:

Format Tersedia

TE091346 Dasar Sistem Pengaturan

Perancangan Kontroler :

Kontroler Proporsional + Integral + Diferensial

Ir. Jos Pramudijanto, M.Eng.

Jurusan Teknik Elektro FTI ITS

Telp. 5947302 Fax.5931237

Email: jos@ee.its.ac.id

Dasar Sistem Pengaturan – 06d 1

Objektif:

Definisi Kontroler PID

Perancangan Kontroler PID

Perancangan Kontroler PID modifikasi

Dasar Sistem Pengaturan – 06d 2

Pengantar

• Kontroler Proporsional ditambah Integral ditambah

Differensial (PID) merupakan kontroler yang aksi

kontrolernya mempunyai sifat proporsional, integral dan

differensial terhadap sinyal kesalahan.

• Pada bagian ini kita akan membahas mengenai prosedur

perancangan kontroler proporsional ditambah integral

ditambah differensial untuk diterapkan pada plant orde

kedua tanpa delay.

• Dengan menentukan nilai penguatan proporsional Kp,

waktu integral τ i dan waktu differensial τ d yang tepat

diharapkan respon plant orde kedua tanpa delay sesuai

dengan spesifikasi performansi yang diinginkan.

Dasar Sistem Pengaturan – 06d 3

Komponen Sistem

Plant orde kedua (tanpa delay)

K

1 2 2ξ

s + s +1

ωn2

ωn

K : gain overall

ω n : frekuensi alami tak teredam

ξ : rasio peredaman

Dasar Sistem Pengaturan – 06d 4

Komponen Sistem

Kontroler PID

1

E(s) K p 1 + + τ d s U(s)

τi s

Kp : penguatan proporsional

τi : waktu integral

τd

: waktu differensial

Dasar Sistem Pengaturan – 06d 5

Fungsi Alih Hasil Rancangan

Diagram blok

K

1 1 2 2ξ

K p 1 + + τ d s s + s +1

τ is ωn 2

ωn

Fungsi alih

τ iτ d s + τ i s + 1

2

K

K p

τ is 1 2 s + 2 2 ξ s + 1

C (s) ωn ωn

=

R (s)

τ iτ d s + τ i s + 1

2 K

1 + K p

τ is 1 2 s 2 + 2 ξ s + 1

ωn ω n

Dasar Sistem Pengaturan – 06d 6

Pendekatan Hasil Rancangan

1 2ζ

Jika dipilih τ i τ d = dan τ i =

ωn

2 ωn

maka C (s) K p .K τ i s 1

= =

R ( s ) 1 + K p .K τ i s τ is

+1

KK p

Sistem hasil rancangan merupakan sistem orde

pertama dengan fungsi alih :

C (s) K* τi

= * ; τ =

*

; K* = 1

R(s) τ s + 1 K .K p

τ * : konstanta waktu sistem hasil, K* : gain sistem hasil

Dasar Sistem Pengaturan – 06d 7

Error Steady State Hasil Rancangan

1

• Untuk masukan unit step : r (t ) = 1 .u (t ) → R (s ) =

s

Error steady state : e ss = R ss − C ss

1

R ss = Lim sR (s ) = Lim s = 1

s→0 s→0 s

1

C ss = lim sC ( s ) = lim s = 1

s→0 s→0

s(τ *

s +1)

sehingga,

e ss = 1 − 1

Dasar Sistem Pengaturan – 06d 8

Prosedur Rancangan Kontroler PID

1. Menentukan fungsi alih plant orde kedua

2. Menentukan spesifikasi performansi respon orde

pertama yang diinginkan

3. Menentukan Kp , τ i , dan τd

2ζ

τi =

ωn

1 1

τiτd = ⇔ τd =

ωn 2 2 ξω n

* τi τi 2ξ

τ = ⇔ Kp = =

K .K p τ * .K τ * . ω n .K

Dasar Sistem Pengaturan – 06d 9

Contoh

Plant orde kedua mempunyai fungsi alih :

5

G (s ) =

s 2 + 6 s + 25

Rencanakanlah kontroler PID sedemikian hingga keluaran

sistem hasil mempunyai ts (± 5%) sekitar 2 detik, ess = 0

(zero offset) dan tidak memiliki overshoot.

Penyelesaian :

5

G (s ) = ⇒ ω n = 5 rad / det ; ξ = 0,6 ; K = 0, 2

s 2 + 6 s + 25

Dasar Sistem Pengaturan – 06d 10

Penyelesaian

Konstanta waktu sistem hasil :

2

ts *

(± 5 % ) ≈ 3τ ≈ 2 det ⇔ τ ≈ det

* *

3

Waktu integral :

2ξ 2 (0,6 )

τi = = = 0, 24

ωn 5

Waktu differensial :

1 1 1

τd = = =

2 ξω n 2 (0 ,6 )(5 ) 6

Dasar Sistem Pengaturan – 06d 11

Penyelesaian

Penguatan proporsional :

2ξ 2 (0,6 ) 3,6

Kp = * = = = 1,8

τ . ω n .K (2 3 )(5 )(0,2 ) 2

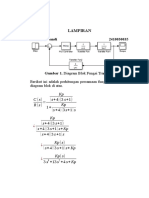

Diagram blok sistem hasil rancangan :

R(s) C(s)

1 1 5

+ - 1,8 1 + + s

0, 24 s 6 s 2 + 6 s + 25

Dasar Sistem Pengaturan – 06d 12

Kontroler PID Modifikasi

• Pada bagian ini kita akan membahas mengenai

prosedur perancangan kontroler proporsional

ditambah integral ditambah differensial modifikasi

untuk diterapkan pada plant orde kedua dengan

delay.

• Dengan menentukan nilai penguatan proporsional

Kp, waktu integral τ i dan waktu differensial τ d 1 , τ d 2.

yang tepat diharapkan respon plant orde kedua

dengan delay sesuai dengan spesifikasi performansi

yang diinginkan.

Dasar Sistem Pengaturan – 06d 13

Komponen Sistem

Plant orde kedua (dengan delay)

K (τs + 1)

1 2 2ξ

s + s +1

ωn2

ωn

K : gain overall

ω n : frekuensi alami tak teredam

ξ : rasio peredaman

τ : time delay

Dasar Sistem Pengaturan – 06d 14

Komponen Sistem

Kontroler PID Modifikasi

1 τ d1s

E(s) K p 1 + + U(s)

τi s τd 2s + 1

Kp : penguatan proporsional

τi: waktu integral

τ d 1 : waktu differensial 1

τ d 2 : waktu differensial 2

Dasar Sistem Pengaturan – 06d 15

Fungsi Alih Hasil Rancangan

Diagram blok

K (τs + 1)

R(s) E(s) τ d 1s U(s) C(s)

+ K p 1 +

1

+ 1 2 2ξ

- s + s +1

τ is τ d 2s + 1 ωn2

ωn

Fungsi alih

C (s )

=

[ ]

KK p τ i (τ d 1 + τ d 2 )s 2 + (τ i + τ d 2 )s + 1 (τs + 1)

1 2 2ξ 2

R(s)

τ i s (τ d 2 s + 1) 2 s +

ωn

[ ]

s + 1 + KK p τ i (τ d 1 + τ d 2 )s 2 + (τ i + τ d 2 )s + 1 (τs + 1)

ωn

Dasar Sistem Pengaturan – 06d 16

Pendekatan Hasil Rancangan

2ζ 1

Dipilih d 2τ = τ , τ i + τ d2 = dan τ i (τ d 1 + τ d 2 ) =

ωn ωn2

C (s) K .K p 1

= =

R ( s ) τ i s + K .K p τi s

+1

KK p

Sistem hasil rancangan merupakan sistem orde

pertama dengan fungsi alih :

C (s) K* τi

= * ; τ =

*

; K* = 1

R(s) τ s + 1 K .K p

τ * : konstanta waktu sistem hasil, K* : gain sistem hasil

Dasar Sistem Pengaturan – 06d 17

Error Steady State Hasil Rancangan

1

• Untuk masukan unit step : r (t ) = 1 .u (t ) → R (s ) =

s

Error steady state : e ss = R ss − C ss

1

R ss = Lim sR (s ) = Lim s = 1

s→0 s→0 s

1

C ss = lim sC ( s ) = lim s =1

s→ 0

( )

s→ 0 s τ * s + 1

sehingga,

e ss = 1 − 1 = 0

Dasar Sistem Pengaturan – 06d 18

Prosedur Rancangan PID Modifikasi

1. Menentukan fungsi alih plant orde kedua

2. Menentukan spesifikasi performansi respon orde

pertama yang diinginkan

3. Menentukan Kp , τ i , τ d 1 dan τ d 1

2ξ 2ξ

τd 2 = τ ; τi + τ d 2 = ⇔ τi = − τ

ωn ωn

1 1

τ i (τ d 1 + τ d 2 ) = 2

⇔ τ d1 = 2

−τ

ωn 2 ξω n − ω n τ

* τi τi 1 2ξ

τ = ⇔ Kp = * = * − τ

K .K p τ .K τ K ωn

Dasar Sistem Pengaturan – 06d 19

Contoh

Plant orde kedua mempunyai fungsi alih :

5(0,1s + 1)

G (s ) =

s 2 + 6 s + 25

Rencanakanlah kontroler proporsional ditambah

integral ditambah differensial sedemikian hingga

keluaran sistem hasil mempunyai ts (± 5%) sekitar 2

detik, zero offset dan tidak memiliki overshoot.

Dasar Sistem Pengaturan – 06d 20

Penyelesaian

Plant merupakan sistem orde dua dengan time delay

Kontroler PID modifikasi

Konstanta waktu sistem hasil :

2

t s (± 5 % ) ≈ 3 τ ≈ 2 det ⇔ τ ≈ det

* * *

3

Waktu differensial 1 : τ d 2 = τ = 0,1 det

Waktu differensial 2 :

1 1

τ d1 = −τ= − 0,1 = 0,19 det

2ξω n − ω n τ 2 (0,6 )(5 ) − (5 ) (0,1)

2 2

Waktu integral : 2ξ 2(0,6)

τi = −τ = − 0,1 = 0,14 det

ωn 5

Dasar Sistem Pengaturan – 06d 21

Penyelesaian

Penguatan proporsional :

1 2ξ

1 2 (0,6 )

Kp = * − τ = − 0,1 = 1,05

τ K ωn (2 3 )(0, 2 ) 5

Diagram blok sistem hasil rancangan :

Dasar Sistem Pengaturan – 06d 22

Ringkasan

1. Suatu plant orde kedua tanpa delay dengan kontroler

proporsional ditambah integral ditambah differensial

(PID) jika dipilih :

1 2ζ

τi τd = 2 dan τi =

ωn ωn

akan menghasilkan sistem orde pertama zero offset

dengan τi

*

τ = dan K * = 1

K .K p

Dasar Sistem Pengaturan – 06d 23

Ringkasan

di mana harga parameter kontrolernya adalah :

2ζ

τi =

ωn

1

τd = , dan

2 ξω n

2ξ

Kp =

ω n .K p

Dasar Sistem Pengaturan – 06d 24

Ringkasan

2. Kontroler proporsional ditambah integral ditambah

differensial modifikasi (PID modifikasi) yang

diterapkan pada plant orde kedua dengan delay jika

dipilih

2ζ 1

τd 2 = τ , τi + τd 2 = , dan τ i (τ d 1 + τ d 2 ) =

ωn ωn2

akan menghasilkan sistem orde pertama zero offset

dengan

τi

*

τ = dan K * = 1

K .K p

Dasar Sistem Pengaturan – 06d 25

Ringkasan

di mana harga parameter kontrolernya adalah :

1

τ d1 = 2

−τ

2 ξω n − ω n τ

τd2 = τ

2ξ

τi = − τ dan

ωn

1 2ξ

Kp = * − τ

τ K ωn

Dasar Sistem Pengaturan – 06d 26

Anda mungkin juga menyukai

- 6e - Desain Kontroler PIDDokumen5 halaman6e - Desain Kontroler PID502.134 Anamta Arrum Sulistyo AjiBelum ada peringkat

- DESAIN KONTROLER PID ORDE DUADokumen6 halamanDESAIN KONTROLER PID ORDE DUAWahyu ArdiansyahBelum ada peringkat

- Desain Kontroler PIDDokumen7 halamanDesain Kontroler PIDFitri NoviyantiBelum ada peringkat

- DesainKontrolerPIDDokumen13 halamanDesainKontrolerPIDAgung FauziBelum ada peringkat

- 6b - Desain Kontroler PIDokumen10 halaman6b - Desain Kontroler PI502.134 Anamta Arrum Sulistyo AjiBelum ada peringkat

- 7.6 Perancangan Pengendali PID PDFDokumen19 halaman7.6 Perancangan Pengendali PID PDFSigit ApriantoBelum ada peringkat

- STABILITAS SISTEMDokumen22 halamanSTABILITAS SISTEMAfifah Nur ChairinnisaBelum ada peringkat

- Desain Kontroler PIDDokumen5 halamanDesain Kontroler PIDMuhammad Yunus AndrianBelum ada peringkat

- PD ModifikasiDokumen15 halamanPD ModifikasiMuhammad RifaiBelum ada peringkat

- Tuning Kontroler PIDDokumen10 halamanTuning Kontroler PIDGregurius DaniswaraBelum ada peringkat

- DESAIN KONTROLER PROPORSIONALDokumen8 halamanDESAIN KONTROLER PROPORSIONALsagatoBelum ada peringkat

- 6 - 7 Desain Kontroler PID Ziegler NicholsDokumen18 halaman6 - 7 Desain Kontroler PID Ziegler NicholsAgung FauziBelum ada peringkat

- Perancangan KontrollerDokumen4 halamanPerancangan KontrollerRAFASS FASBelum ada peringkat

- Analisa Tanggapan Waktu-Ordo 2Dokumen9 halamanAnalisa Tanggapan Waktu-Ordo 2Baiahqi HakimBelum ada peringkat

- Autotuning Sistem KontrolDokumen43 halamanAutotuning Sistem KontrolhendiBelum ada peringkat

- Kendali 4Dokumen9 halamanKendali 4Agus PrionoBelum ada peringkat

- Analisis Sistem KendaliDokumen22 halamanAnalisis Sistem KendalifachriyansyahBelum ada peringkat

- Soal-soal Latihan UAS Teknik KendaliDokumen6 halamanSoal-soal Latihan UAS Teknik KendalikuhakuBelum ada peringkat

- StepResponseDokumen10 halamanStepResponseRidwanBelum ada peringkat

- 09 Sensitivitas Dan AkurasiDokumen25 halaman09 Sensitivitas Dan AkurasiFILDANY MUHADZDZIB SALSABIL 180536633042Belum ada peringkat

- Kuis Instrumentasi Dan Pengendalian ProsesDokumen4 halamanKuis Instrumentasi Dan Pengendalian ProsesgaryBelum ada peringkat

- FNAL P1 Idris-1Dokumen39 halamanFNAL P1 Idris-1EDUZAR ZARBelum ada peringkat

- Algoritma D and CDokumen115 halamanAlgoritma D and CDanu Ahmad MaulanaBelum ada peringkat

- Kestabilan Sistem 7Dokumen7 halamanKestabilan Sistem 7ANNISYA RAHAYUBelum ada peringkat

- Tuning Kontroler PIDDokumen9 halamanTuning Kontroler PIDchoiozaBelum ada peringkat

- Ziegler-Nichols PIDDokumen8 halamanZiegler-Nichols PIDsagatoBelum ada peringkat

- Estimasi Sistem Orde Satu Tambah Waktu Tunda (OSTWT)Dokumen50 halamanEstimasi Sistem Orde Satu Tambah Waktu Tunda (OSTWT)M FebriansyahBelum ada peringkat

- Bagian - 3 Dinamika Proses Sistem Sederhana - 2019 PDFDokumen35 halamanBagian - 3 Dinamika Proses Sistem Sederhana - 2019 PDFTabitaKristinaBelum ada peringkat

- Tubes - Siskon B - Kelompok 3Dokumen16 halamanTubes - Siskon B - Kelompok 3Zufar Yusuf Putra ViandhiBelum ada peringkat

- 06 - Desain Sistem KendaliDokumen27 halaman06 - Desain Sistem Kendalimuchtar antonioBelum ada peringkat

- Tugas Peng2 MuslimDokumen9 halamanTugas Peng2 MuslimMuslim FirnandaBelum ada peringkat

- Tugas Peng2 MuslimDokumen9 halamanTugas Peng2 MuslimMuslim FirnandaBelum ada peringkat

- Orde 1 2Dokumen2 halamanOrde 1 2Widya Primaswari PutriBelum ada peringkat

- Operasi Konvolusi Sinyal Diskrit Dengan MATLABDokumen10 halamanOperasi Konvolusi Sinyal Diskrit Dengan MATLABFerdy Rahmat HidayatBelum ada peringkat

- Analisa Kestabilan Sistem Menggunakan MeDokumen20 halamanAnalisa Kestabilan Sistem Menggunakan MeIik IkhsanBelum ada peringkat

- KARAKTERISTIK SISTEM ORDE KEDUADokumen12 halamanKARAKTERISTIK SISTEM ORDE KEDUAmuhammad fauzan100% (1)

- SIMULASI-KONTROLDokumen17 halamanSIMULASI-KONTROLDina SiltriBelum ada peringkat

- Kendali PidDokumen10 halamanKendali Pidjessyana tambunanBelum ada peringkat

- Laporan TSK - Kestabilan Sistem - Fadlilah Husaini 21130063Dokumen7 halamanLaporan TSK - Kestabilan Sistem - Fadlilah Husaini 21130063Ksatria NugrahaBelum ada peringkat

- (Dokumen-129) Modul Praktikum Dasar Sistem Kendali S1 RegulerDokumen27 halaman(Dokumen-129) Modul Praktikum Dasar Sistem Kendali S1 RegulerIkhsan TaufikBelum ada peringkat

- 7.6 Perancangan Pengendali PIDDokumen19 halaman7.6 Perancangan Pengendali PIDDhikri SuprayogaBelum ada peringkat

- Modul6 Sistem LinierDokumen10 halamanModul6 Sistem LinierSetyawan EdyBelum ada peringkat

- Kertas Jawaban UjianDokumen4 halamanKertas Jawaban Ujianbudi sugiartoBelum ada peringkat

- Dasar Sistem Kontrol DanDokumen47 halamanDasar Sistem Kontrol Dannur narangBelum ada peringkat

- OPTIMASI PIDDokumen4 halamanOPTIMASI PIDReyOktBelum ada peringkat

- ANALISIS KESALAHANDokumen14 halamanANALISIS KESALAHANRizkiBelum ada peringkat

- Desain Kontroler PIDokumen10 halamanDesain Kontroler PIrakaBelum ada peringkat

- Analisis Respons Sistem Kontrol PID Dengan MATLABDokumen29 halamanAnalisis Respons Sistem Kontrol PID Dengan MATLABIRpan IRyandiBelum ada peringkat

- Pemodelan Juanli M. Taroreh - f44120090Dokumen4 halamanPemodelan Juanli M. Taroreh - f44120090Juanli m. TarorehBelum ada peringkat

- P. Anzar M.praktikum K.diskritDokumen10 halamanP. Anzar M.praktikum K.diskritrinthamelisaguloBelum ada peringkat

- Fungsi Alih Orde 2Dokumen10 halamanFungsi Alih Orde 2Riki PkdBelum ada peringkat

- Fungsi Alih Orde 2Dokumen10 halamanFungsi Alih Orde 2adiBelum ada peringkat

- Determinan Struktur Modal Bank: Oleh: Siti MuarifahDokumen10 halamanDeterminan Struktur Modal Bank: Oleh: Siti Muarifahharis kunkunBelum ada peringkat

- Determinan Struktur Modal Bank: Oleh: Siti MuarifahDokumen10 halamanDeterminan Struktur Modal Bank: Oleh: Siti Muarifahharis kunkunBelum ada peringkat

- Sari Kacang HijauDokumen3 halamanSari Kacang Hijauharis kunkunBelum ada peringkat

- SPT - LidiyaDokumen11 halamanSPT - Lidiyaharis kunkunBelum ada peringkat

- Tugas2 - SPT - Anis Zakiyyah FDokumen10 halamanTugas2 - SPT - Anis Zakiyyah Fharis kunkunBelum ada peringkat

- UTS 2020-2021 Multivariat Untuk Pebisnis Ahmad Haris Kurnia Dwiputera 190820101037Dokumen3 halamanUTS 2020-2021 Multivariat Untuk Pebisnis Ahmad Haris Kurnia Dwiputera 190820101037haris kunkunBelum ada peringkat

- Statistika UTS Fakultas EkonomiDokumen6 halamanStatistika UTS Fakultas Ekonomiharis kunkunBelum ada peringkat

- Tugas2 - SPT - Anis Zakiyyah FDokumen10 halamanTugas2 - SPT - Anis Zakiyyah Fharis kunkunBelum ada peringkat

- Rencana Tesis Aprilla PristiDokumen9 halamanRencana Tesis Aprilla Pristiharis kunkunBelum ada peringkat

- Pernyataan DiriDokumen1 halamanPernyataan DiriAnonymous v6ak7rmBelum ada peringkat

- Sustaining Competitiive AdvantageDokumen17 halamanSustaining Competitiive Advantageharis kunkunBelum ada peringkat

- OPTIMASI PDB NUMERIKDokumen15 halamanOPTIMASI PDB NUMERIKAstrid HerawatiBelum ada peringkat

- Kopi Susu 1 LiterDokumen3 halamanKopi Susu 1 Literharis kunkunBelum ada peringkat

- BAserahterimaDokumen2 halamanBAserahterimaLee Xian JingBelum ada peringkat

- Jadwal RancangDokumen62 halamanJadwal Rancangharis kunkunBelum ada peringkat

- Surat PernyataanDokumen2 halamanSurat PernyataanEpy Jacob KurangkerjaBelum ada peringkat

- MamasukaDokumen6 halamanMamasukaharis kunkunBelum ada peringkat

- Review Mbak QoniDokumen1 halamanReview Mbak Qoniharis kunkunBelum ada peringkat

- Bab V Pemeliharaan UnitDokumen3 halamanBab V Pemeliharaan Unitharis kunkunBelum ada peringkat

- Proposal Transien Rev 2Dokumen5 halamanProposal Transien Rev 2haris kunkunBelum ada peringkat

- TUGAS3 QUIZ - Faisal Adhisthana N - 2210 100 054Dokumen5 halamanTUGAS3 QUIZ - Faisal Adhisthana N - 2210 100 054haris kunkunBelum ada peringkat

- Bab 8 Solusi Persamaan Diferensial BiasaDokumen60 halamanBab 8 Solusi Persamaan Diferensial Biasabenny_050% (2)

- Tugas IDokumen3 halamanTugas Iharis kunkunBelum ada peringkat

- LEMBAR PENGESAHAN 2 (Blmfix)Dokumen1 halamanLEMBAR PENGESAHAN 2 (Blmfix)haris kunkunBelum ada peringkat

- Lembar Pengesahan 1 FixDokumen1 halamanLembar Pengesahan 1 Fixharis kunkunBelum ada peringkat

- Lembar Pengesahan 1 FixDokumen1 halamanLembar Pengesahan 1 Fixharis kunkunBelum ada peringkat

- Kata PengantarDokumen2 halamanKata Pengantarharis kunkunBelum ada peringkat

- Metode Numerik Secara UmumDokumen15 halamanMetode Numerik Secara UmumSeptian Dwi NurcahyadiBelum ada peringkat

- LEMBAR PENGESAHAN 2 (Blmfix)Dokumen1 halamanLEMBAR PENGESAHAN 2 (Blmfix)haris kunkunBelum ada peringkat