0% menganggap dokumen ini bermanfaat (0 suara)

815 tayangan3 halamanDecoder 3 TO 8

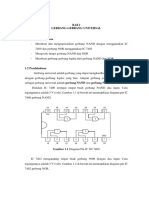

Dokumen tersebut membahas tentang decoder 3 ke 8 yang berfungsi untuk mengubah kode masukan 3 bit menjadi 8 keluaran. Dijelaskan prinsip kerja decoder menggunakan gate logika NAND dan tabel kebenaran operasinya. Diuraikan pula rangkaian praktik decoder 3 ke 8 beserta simulasinya untuk menganalisis keluaran berdasarkan kombinasi input.

Diunggah oleh

Rabel TariganHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai PDF, TXT atau baca online di Scribd

0% menganggap dokumen ini bermanfaat (0 suara)

815 tayangan3 halamanDecoder 3 TO 8

Dokumen tersebut membahas tentang decoder 3 ke 8 yang berfungsi untuk mengubah kode masukan 3 bit menjadi 8 keluaran. Dijelaskan prinsip kerja decoder menggunakan gate logika NAND dan tabel kebenaran operasinya. Diuraikan pula rangkaian praktik decoder 3 ke 8 beserta simulasinya untuk menganalisis keluaran berdasarkan kombinasi input.

Diunggah oleh

Rabel TariganHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai PDF, TXT atau baca online di Scribd