0% menganggap dokumen ini bermanfaat (0 suara)

65 tayangan8 halamanPanduan Shift Register Digital 4 Bit

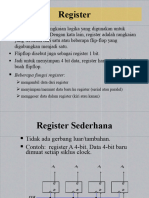

Bab V dokumen tersebut membahas tentang shift register, yaitu rangkaian logika yang dapat menyimpan dan mengolah informasi digital sementara dengan cara menggeser data satu bit ke kiri atau kanan setiap menerima pulsa clock. Terdapat beberapa jenis shift register berdasarkan cara masukan dan keluarnya data, seperti serial in serial out, serial in paralel out, paralel in serial out, dan paralel in paralel out."

Diunggah oleh

VaiNz LuINeHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai PDF, TXT atau baca online di Scribd

0% menganggap dokumen ini bermanfaat (0 suara)

65 tayangan8 halamanPanduan Shift Register Digital 4 Bit

Bab V dokumen tersebut membahas tentang shift register, yaitu rangkaian logika yang dapat menyimpan dan mengolah informasi digital sementara dengan cara menggeser data satu bit ke kiri atau kanan setiap menerima pulsa clock. Terdapat beberapa jenis shift register berdasarkan cara masukan dan keluarnya data, seperti serial in serial out, serial in paralel out, paralel in serial out, dan paralel in paralel out."

Diunggah oleh

VaiNz LuINeHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai PDF, TXT atau baca online di Scribd